Эффективность выполнения инструкций

- Цикл работы процессора:

Загрузка инструкции (IF = Instruction Fetch)

Декодирование инструкции, выделение команды и операндов, чтение регистров (ID = Instruction Decode)

Фактическое выполнение инструкции (Ex = Execute)

Сохранение регистра в память, Загрузка регистра из памяти (MEM = Memory access)

Запись результата регистр (WB = Writeback)

- Мысленный эксперимент.

- Предположим существует возможность создать для каждой стадии цикла исполнения инструкции полностью автономное устройство(микросхему или часть микосхемы). Предположим также, что эти устройства могут быть последовательно связаны. Тогда для вычисления одной инструкции понадобится целых пять циклов.

НО:

- Мы можем повысить тактовую частоту, поскольку максимальная задержка теперь стала меньше.

- Во время каждого цикла мы можем использовать все части тракта данных.

Принципиальная схема MARS. => параллельная загрузка узлов

- Конвейер

- В RISC-ядре процессора реализован конвейер, состоящий из пяти стадий и аналогичный конвейеру ядра R3000. Конвейер дает возможность процессору работать на высокой частоте, при этом минимизируется сложность устройства, а также уменьшается стоимость и потребление энергии.

- Стадии конвейера

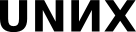

- Конвейер содержит пять стадий: На Рисунке 1 показаны операции, выполняемые CPU-ядром на каждом этапе конвейера.

- Стадия I: выборка команды

- На этой стадии команда выбирается из командного кэша.

- Стадия D: дешифрация команды

- На этой стадии:

- Операнды выбираются из регистрового файла.

- Операнды передаются на эту стадию со стадий E, M и W.

- ALU определяет, выполняется ли условие перехода и вычисляет виртуальный адрес перехода для команд перехода.

- Осуществляется преобразование виртуального адреса в физический.

- Производится поиск адреса команды по TLB и вырабатывается признак hit/miss.

- Командная логика выбирает адрес команды.

- На этой стадии:

- Стадия E: исполнение

- На этой стадии:

- ALU выполняет арифметические или логические операции для команд типа регистр-регистр.

- Производится преобразование виртуального адреса в физический для данных, используемых командами загрузки и сохранения.

- Производится поиск данных по TLB и вырабатывается признак hit/miss.

- Все операции умножения и деления выполняются на этой стадии.

- На этой стадии:

- Стадия M: выборка из памяти

- На этой стадии осуществляется загрузка и выравнивание загруженных данных в границах слова.

- Стадия W: обратная запись

- На этой стадии для команд типа регистр-регистр или для команд загрузки результат записывается обратно в регистровый файл.

- Конвейер содержит пять стадий: На Рисунке 1 показаны операции, выполняемые CPU-ядром на каждом этапе конвейера.

- Операции умножения и деления

- Время выполнения этих операций соответствует 17 тактам для команд умножения и 18 тактам для команд умножения с накоплением, а также 33 тактам для команд деления и 34 тактам для команд деления с накоплением.

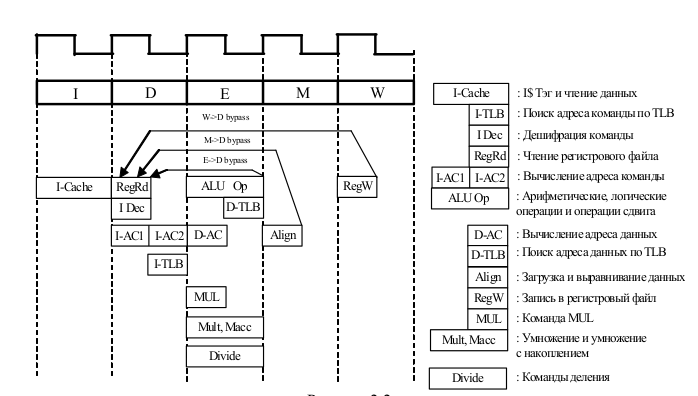

- Задержка выполнения команд перехода (Jump, Branch)

- Конвейер осуществляет выполнение команд перехода с задержкой в один такт. Однотактная задержка является результатом функционирования логики, ответственной за принятие решения о переходе на стадии D конвейера. Эта задержка позволяет использовать адрес перехода, вычисленный на предыдущей стадии, для доступа к команде на следующей D-стадии. Слот задержки перехода (branch delay slot) позволяет отказаться от остановок конвейера при переходе. Вычисление адреса и проверка условия перехода выполняются одновременно на стадии D. Итоговое значение PC (счетчика команд) используется для выборки очередной команды на стадии I, которая является второй командой после перехода. На Рисунок 2 показан слот задержки перехода.

- Конвейер осуществляет выполнение команд перехода с задержкой в один такт. Однотактная задержка является результатом функционирования логики, ответственной за принятие решения о переходе на стадии D конвейера. Эта задержка позволяет использовать адрес перехода, вычисленный на предыдущей стадии, для доступа к команде на следующей D-стадии. Слот задержки перехода (branch delay slot) позволяет отказаться от остановок конвейера при переходе. Вычисление адреса и проверка условия перехода выполняются одновременно на стадии D. Итоговое значение PC (счетчика команд) используется для выборки очередной команды на стадии I, которая является второй командой после перехода. На Рисунок 2 показан слот задержки перехода.

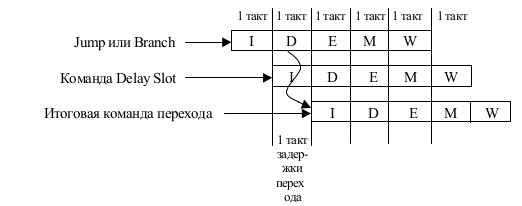

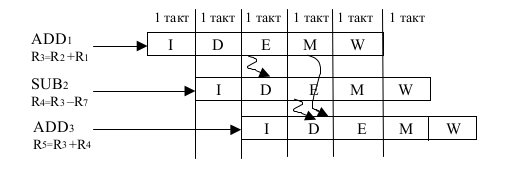

- Обходные пути передачи данных (Data bypass)

Для большинства команд MIPS32 исходными операндами являются значения, хранящиеся в регистрах общего назначения. Эти операнды выбираются из регистрового файла в первой половине D-стадии. После исполнения на ALU результат, в принципе, готов для использования другими командами. Но запись результата в регистровый файл существляется только на стадии W. Это лишает следующую команду возможности использовать результат в течение 3-х циклов, если ее операндом является результат выполнения последней операции, сохраненный в регистровом файле. Для преодоления этой проблемы используются обходные пути передачи данных. Мультиплексоры обходных путей передачи данных для обоих операндов располагаются между регистровым файлом и ALU (Рисунок 3). Они позволяют передавать данные с выхода стадий E, M и W конвейера прямо на стадию D, если один из регистров источника (source) декодируемой команды совпадает с регистром назначения (target) одной из предшествующих команд. Входы мультиплексоров подключены к обходным путям M->D и E->D, а также W->D.

На Рисунке 4 показаны обходные пути передачи данных для команды Add 1 , за которой следует команда Sub 2 и затем снова Add 3 . Поскольку команда Sub 2 в качестве одного из операндов использует результат операции Add 1 , используется обходной путь E->D. Следующая команда Add 3 использует результаты обеих предшествующих операций: Add 1 и Sub 2 . Так как данные команды Add 1 в это время находятся на стадии M, используется обходной путь M->D. Кроме того, вновь используется обходной путь E->D для передачи результата операции Sub 2 команде Add 3 .

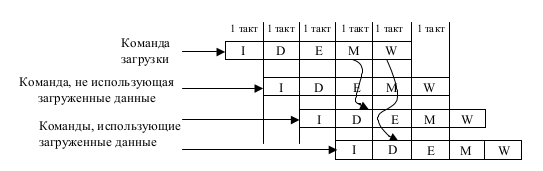

- Задержка загрузки данных

Данные, выбираемые командами загрузки (Load), становятся доступными на конвейере только после выравнивания на стадии M. При этом данные, являющиеся исходными операндами, должны предоставляться командам для обработки уже на стадии D. Поэтому, если сразу за командой загрузки следует команда, для которой один из регистров исходных операндов совпадает с регистром, в который производится загрузка данных, это вызывает приостановку в работе конвейера на стадии D. Эта приостановка осуществляется аппаратной вставкой команды NOP. Во время этой задержки часть конвейера, которая находится дальше стадии D, продолжает продвигаться. Если же команда, использующая загружаемые данные, следует за командой загрузки не сразу, а через одну или через две, то для обеспечения бесперебойной работы конвейера используется один из обходных путей передачи данных: M->D или W->D (Рисунок 5).

- Пример конвейера на MIPS

- Конфликт по данным

- Конфликт по управлению

- Варианты:

- не обнаруживать (пускай компилятор думает)

- обнаруживать (процессор)

- переупорядочивать микрокоманды

- возможно, сразу нескольких инструкций, если они развязаны (суперскалярность)

- использовать несколько вычисляющих устройств для развязанных по данным команд (векторность)

- опережающее выполнение, предсказание по переходам и т. д.

- Дополнение.

- Архитектура MIPS предусматривает два типа блокировок:

- Stall – конвейер останавливается полностью и ожидает снятия блокировки;

- Slip – останавливается только часть конвейера – ступень, которая вызвала блокировку, и все более ранние ступени. Более поздние ступени завершаются. Например, при блоки ровке стадии E более поздние стадии M и W могут быть завершены. При этом до снятия блокировки на стадии E конвейер вставляет пустые команды NOP на стадии A и W, которые также называются bubble.

UPD Предполагается, что условный переход не происходит, что важно для циклов.

- Архитектура MIPS предусматривает два типа блокировок: