Лекция 1 (2012-10-15)

О чём этот курс, его содержание

Спецкурс кафедры АСВК, семестровый, в конце экзамен, форма экзамена скорее всего письменно-устная, но точно пока неизвестно.

В курсе предполагается рассказать то, что не затрагивается в других курсах, читаемых на факультете. Базируется на знаниях, полученных в процессе занятий реальными вещами после окончания университета.

Будут затронуты такие темы как физические основы построения ЭВМ с точки зрения того, что удалось достигнуть сейчас, флоу построения процессора и чипа, как вообще организован чип, x86, arm, power, mips — текущее состояние. Как организованы современные платформы и как происходит взаимодействие внутри них. Особое внимание периферии, так как интерфейсы требуют всё больших вычислительных ресурсов. Интеграция интерф общения с периферийными устройствами (сетевые адаптеры, видеокарты, и т.п.) на спарках, и не только, например, уже интегрированы в сам процессор. Вопросы подключения ускорителей. Мобильные платформы и вопросы энергосбережения.

Сегодняшняя лекция про то, как эти самые ЭВМ устроены, как напаяны эти самые страшные провода и чипы. Рассказ будет несколько фрагментарен, но лектор надеется, что этого будет достаточно для понимания, как оно вообще работает.

Голодный минимум

Не будем начинать с пафосных речей о том, что такое информация. Начнём с того, что у нас есть биты — два различимых состояния, которые надо хранить, передавать и обрабатывать.

Всё это можно делать различными способами. Механический — счёты, машина Бэббиджа, калькулятор Паскаля. Состояния дискретны. Сложны в реализации. Бэббидж, например, так и не смог добиться нужного качества шестерёнок. Механика и в современных системах зачастую лимитрует производительность. Например, скорость произвольного доступа к жесткому диску упирается в механику. Хотя, вся механика заключается только в движении головки. Более механическая core memory, где магнитные сердечники нанизываются на пересечения проводов, запоминая бешеные килобиты-мегабиты информации, при том, что современные им жёсткие диски были ёмкостью десятки мегабайт. Чем меньше механики, тем лучше, используем электромагнитизм во благо человечества.

Схема зажигания лампочки магнитной катушкой — пускаем ток, катушка намагничивается, притягивает металический язычок, который замыкает контур и даёт ток лампочке.

Если два таких реле соединить последовательно, то лампочка загорится, только если оба ключа замкнуты. Таким образом, мы изобрели логический элемент «И», и можем себя с этим поздравить. Аналогично, можем включить реле параллельно и получить элемент «ИЛИ». Реле — это один из способов организации схем, которые использовались в конце 40-х годов, потом перешли на лампы, потом на транзисторы. На реле зато очень удобно все показывать — ток пустили, лампочка загорелась, всё понятно.

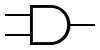

Далее будут использоваться следующие обозначения логических вентилей:

И

И  ИЛИ

ИЛИ

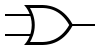

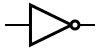

По аналогии можно сконструировать другие логические примитивы — буфер, отрицание, исключающее или, или-не, и-не:

БУФЕР

БУФЕР  НЕ

НЕ  НЕ-И

НЕ-И  НЕ-ИЛИ

НЕ-ИЛИ  ИСКЛ_ИЛИ

ИСКЛ_ИЛИ  НЕ-ИСКЛ_ИЛИ

НЕ-ИСКЛ_ИЛИ

Описание логических вентилей в википедии

У подобных схем есть некоторое время срабатывания. Оно, вообще говоря, зависит от массо-габаритных характеристик реле. Поэтому вводится элемент буфер (простейшая конструкция — два последовательно соединенных отрицания). В основном он нужен для выравнивания потоков, когда один идёт по сложной схеме, а второй по простой, и надо их синхронизировать.

Так же вводятся сумматор и полусумматор ( как на курсе основы кибернетики).

Полусумматор (A, B — входы, S — выход, C (carry-bit) — бит переноса):

И сумматор:

Если сделаем извращение и зациклим NOT, то это будет очень странная схема, но она будет иметь право на существование. Получим генератор автоколебаний (тактовой частоты) . PLL(phase locked loop) и DLL (delay locked loop). Имея такой генератор, можно им тактировать разные схемы.

Из двух модулей или-не можем собрать штуку, работающую довольно интересным способом:

Два ключа разомкнуты — лампочка не горит. Замыкаем вход один вход один раз, потом размыкаем, а лампочка продолжает гореть (за счет того, что или на входе достаточно всего одной 1). Схема запомнила свое состояние. Если замкнем один раз другой вход, лампочка погаснет. Такая несложная схема называется latch, или защелка. Это базовый элемент различных схем. Все подобные схемы называются flip-flop (тригеры). Из википедии — простые элементы, запоминающие состояния, обычно называют защелками. Элементы, запоминающие состояния и включающие в себя генератор тактовой частоты (clocked devices) называют триггерами (flip-flops).

Чтобы из этого сделать что-то интересное, добавим защёлку по уровню(Gated D latch):

У простой защёлки два входа, но ток мы подавали либо на один, либо на второй. Логично попробовать сделать нечто, где это "либо-либо" определяется одним входным битом. Защёлка по уровню получается из простой защёлки тем, что

к схеме добавляется разветвитель, у которого один вход (D) и два выхода: D и отрицание D.

так же добавляется вход E (write-enable, clock, control). Если E=1, то защелка передает D на свой выход Q, и, соответственно, отрицание D на свой второй выход. Если E=0, то защелка остается в неизменном запомненном состоянии, чтобы не происходило с D.

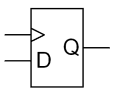

Обозначение защелки по уровню:

Таблица истинности для защелки по уровню:

E |

D |

Q |

!Q |

0 |

любое |

предыдущее Q |

предыдущее !Q |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

Защёлки по уровню необходимы, в частности, при сопряжении наборов логики, тактирующихся различными генераторами тактовой частоты.

Следующий необходимый нам элемент — защёлка с срабатыванием по фронту (positive-edge triggered master–slave D flip-flop):

Защёлка со срабатывание по фронту получается, фактически, соединением двух защелок с срабатыванием по уровню и добавления в правильные места инвертеров.

Обозначение на схемах:

Таблица истинности:

Clock |

D |

Q_next |

Превращается из 0 в 1 |

0 |

0 |

Превращается из 0 в 1 |

1 |

1 |

Не превращается из 0 в 1 |

X |

Q |

В момент переключения сигнала C из 0 в 1 мы запомнили вход D. Будем использовать, когда будем рассматривать всякие периферийные шины. Когда клок начинает подниматься из 0 в 1, берётся состояние со всех входов, а в остальное время там ещё идут всякие переходные процессы. Например, шина PCI на этом играет.

У защёлки по уровню переименуем входы в write-enable и data-input, а выход оставим один, назвав data-output. Вот у нас ячейка памяти в один бит.

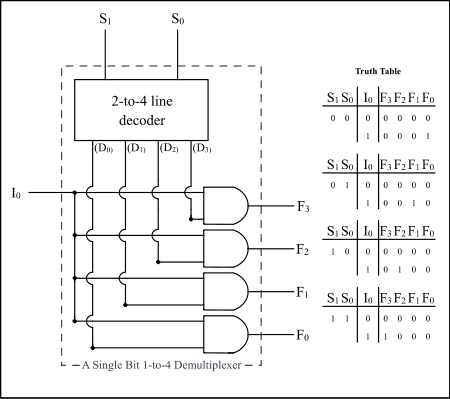

Итак, у нас есть память. Чтобы иметь доступ, надо к ней адресоваться. Чтобы адресоваться сделаем ещё одну простенькую схему. Возьмем таких ячеек много, например, 4. Допустим, мы хотим их читать последовательно. У нас два бита на адрес. На входе адрес надо дешифровывать, чтобы понять, из какой именно ячейки брать окончательный DataOutput.

Есть две волшебных коробочки — дешифратор и селектор.

Пример дешифратора для 2 битов адреса и 4 выходов (позволяет по адресу подать напряжение на нужный выход):

Пример селектора для 2 битов адреса и 4 информационных входов (позволяет оттранслировать на выход вход с номером, соответствующим адресу):

Из селектора, дешифратора и ячеек памяти собирается блок памяти.

Из D-type latch с переключением по фронту можно собрать уменьшитель тактовой частоты в два раза.

Если собрать их несколько, то можно получить счётчик тактов. Полезная штука.

Это голодный минимум, который нам потребуется дальше при рассмотрении архитектуры процессоров.

Ещё немножко поговорим про воркфлоу разработки чипов и, наверное, на этом и закончим.

Воркфлоу разработки чипа

В Sandy Bridge’e порядка 2-x миллиардов транзисторов. Из них 30 процентов только память. И вы видели, как это всё соединено — даже селектор 4 на 1 уже было не очень понятно, а в более сложной логике все ещё страшнее. Логика в десятки, сотни, тысячи элементов ещё обозрима умом (так делалось в 50-е годы), то сейчас умом это уже не обозримо, и есть воркфлоу разработки, начиная от относительно высокоуровнего system-c и вплоть до топологии. Когда у вас уже нарисованы все дорожки, просчитаны все задержки, и на всех уровнях у вас происходит верификация, что вы укладываетесь в необходимое время.

Сначала появляется некая идея про то, что должен делать чип. Разрабатывается спецификация, разрабатывается архитектура.

Архитектура. На этом уровне определеяется функциональность создаваемого чипа, создается спецификация. Осуществляются начальные этапы формальной верификации.

Модель. Задается высокоуровневое описание того, как будет реализовываться указанная в спецификации функциональность. Чаще всего используется язык проектирования и верификации моделей системного уровняSystemC

'''Netlist''' (описание графовой структуры) + '''SDF''' (привязка к временным ограничениям, time constraints)

Place&Routing. Есть чудесный граф без привязки к реальной жизни, что создать соответствующую ему интегральную схему, его надо разложить на несколько плоскостей, чтобы ничего не пересекалось и лежало красиво, и соблюдались time-constraints. Сказали гигагерц — должна вся логика за наносекунду переключаться. В связи с этим, кэш 2-3 уровня обычно работает на какой-то части от основной частоты (потому что дешифраторы/селекторы там большие слишком).

Floor Planning — примерный дизайн расположения основных блоков, чтобы раскладывать не два миллиарда транзисторов за раз, а отдельно каждый блок, каждый из блоков по 100-10 миллионов транзисторов.

DFT. После того, как вы полили несчастную кремниевую пластину кучей химикатов, у вас есть некий процент негодных чипов. Эти негодные чипы хочется выявлять как можно раньше. Пластину режут, потом клеят на подложку. Изготовление подложек процесс нетривиальный, и тратить их на негодные чипы не хочется. Актуален вопрос отсеивания бракованных чипов сразу после разрезания. DFT (Design for testability) — базовые проверки на то, что логика переключается, итп. Это тест именно работоспособности чипа, а не его функциональности.

PLOC (pin location) package от того куда вы какие дорожки выведете будет зависеть то, как удобно у вас будет дизайнится печатная плата (PCB). Pentium 4 требовал 10 слоёв подложки, например. Тогда же выравниваются дорожки. Разбегание дорожек skew, его нужно компенсировать на PCB.

Power. Оценка power consumption, TDP.

В следующий раз про архитектуры различных платформ и немножко про процессор изнутри.

Дополнительная часть

На самом деле никаких нулей и единиц не существует. Сушествуют high и low, которые условно считаются 1 и 0. Пусть номинальное напряжение у нас 5 вольт. 0—0.8 считаем 0, 2.2—5 — единицей, а что между ними? Между ними x. На некоторых этапах симуляции мы допускаем на входе что-то неизвестное.

PCIe 3.0 8 GT/s 125 ps^(-1)

Дергать напряжение с такой скоростью — задача затруднительная. В реальной жизни идут всякие переходные процессы. Сейчас рассказывается обзорная штука, ничего строго.

TTT74xx — библиотека логических элементов.

Хотим подавать какой-то сигнал, например 0111010. Реальный график напряжения будет весьма гладкий, поэтому надо предвосхищать смену значений — pre-emphasis — преусиление (преискажение) и post-emphasis. Тогда мы сможем начать передавать что-то похожее на тот сигнал, который мы хотим передавать.

Реально увидеть этот график сложно, поэтому смотрят на eye-diadram — гонят по проводу большое количество данных и смотрят, какая картина происходит статистически, определяя, как часто мы попадаем в значимые значения, а как часто в молоко.

Differential pair.

Машинерией считывания сигнала занимается serdes — serialiser deserialiser.

Это все был трансмиттер.

На приеме приезжает страшный, измученный искажениями сигнал, к которому обычно применяется следующее:

- отсеять гармоники. Самый простой способ — использовать комбинацию активного сопротивления и индуктивнусть и ёмкостное сопротивление такие, что они будут минимальны именно на частоте приемника. Другой способ — использовать decision feedback eq. Используем автоподстройку усиления.